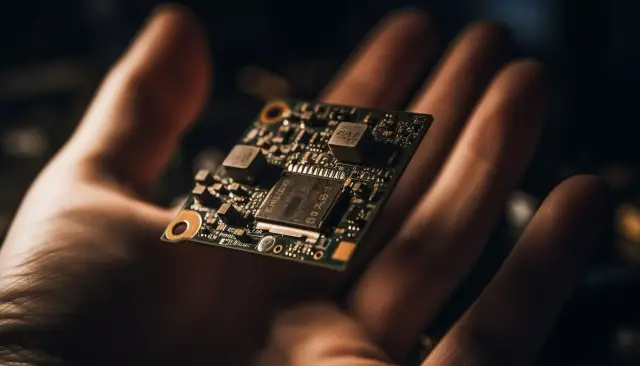

IBM Research Europe revela chip de computação em memória com sinal misto de 64 núcleos revolucionário

A IBM Research Europe apresenta um inovador chip de computação de memória mista de 64 núcleos. Baseado em dispositivos de memória de mudança de fase, o chip foi projetado para aprimorar os cálculos de redes neurais profundas, reduzindo substancialmente os períodos de computação e o consumo de energia.

Os cientistas da IBM Research Europe foram recentemente pioneiros num novo domínio na computação in-memory com o seu chip de 64 núcleos que depende de dispositivos de memória de mudança de fase. Esta tecnologia de ponta foi projetada para impulsionar o funcionamento de redes neurais profundas, mantendo a precisão dos algoritmos de aprendizagem profunda e, ao mesmo tempo, minimizando significativamente os períodos de computação e o consumo de energia.

Manuel Le Gallo, coautor do artigo de pesquisa inovador, compartilhou que eles vêm explorando dispositivos de memória de mudança de fase (PCM) para computação há mais de sete anos. A jornada começou com a equipe demonstrando a implementação de funções neuronais usando dispositivos PCM individuais. Deste ponto em diante, a IBM Research Europe demonstrou que os dispositivos PCM podem beneficiar enormemente os domínios da computação, como a computação científica e a inferência de redes neurais profundas. Com seu chip mais recente, os pesquisadores deram um passo mais perto de um acelerador de inferência analógico de ponta a ponta.

Le Gallo e seus colaboradores conseguiram esse feito sintetizando núcleos baseados em PCM com processadores de computação digital. Estes dois elementos foram ligados através da implementação de uma rede de comunicação digital on-chip. O chip resultante é um amálgama inovador de 64 núcleos analógicos baseados em PCM, cada um incorporando um conjunto de células unitárias sinápticas de 256 por 256 barras transversais.

A integração de conversores analógico-digitais compactos e baseados em tempo dentro de cada núcleo marcou uma transição entre os domínios analógico e digital. Le Gallo explicou ainda, acrescentando que cada núcleo também compreende unidades de processamento digital leves que realizam funções de ativação neuronal de unidade linear retificada (reLU) e operações de escalonamento. Além disso, o chip possui uma unidade de processamento digital global localizada em seu centro que facilita as operações de rede de memória de longo e curto prazo (LSTM).

Uma característica engenhosa do chip de computação in-memory da IBM é a conexão entre os núcleos de memória e sua unidade de processamento localizada globalmente por meio de uma rede de comunicação digital. Esse design permite que o chip execute todos os cálculos associados às camadas individuais de uma rede neural no chip, o que resulta em reduções drásticas nos tempos de computação e no consumo de energia.

Para avaliar a eficácia do novo chip, a equipe de pesquisa da IBM conduziu um estudo abrangente, aplicando algoritmos de aprendizagem profunda em seu chip e avaliando seu desempenho. Os resultados foram encorajadores, com redes neurais profundas treinadas no conjunto de dados de imagens CIFAR-10 para tarefas de reconhecimento de imagens alcançando uma excelente taxa de precisão de 92,81% quando executadas no chip.

Sem dúvida, as realizações da IBM Research Europe são um salto em frente no desenvolvimento de chips Analog In-Memory Computing (AIMC) que podem atender de forma eficiente aos requisitos e desafios dos algoritmos de aprendizagem profunda. Nos próximos anos, a arquitetura introduzida por Le Gallo e sua equipe poderá ser aprimorada para produzir um desempenho ainda superior.

Apesar do avanço da IBM, os potenciais casos de utilização desta tecnologia no ambiente no-code e low-code não podem ser ignorados. Os chips de computação em memória escaláveis e de alto desempenho oferecem um valor considerável ao se integrarem perfeitamente com plataformas no-code como AppMaster. Essa integração poderia resultar em uma melhoria significativa na precisão dos modelos em implementações de aprendizado de máquina, oferecendo menor latência, velocidades mais altas e maior eficiência aos usuários.